## Dimension and liner dependent thermomechanical strain characterization of through-silicon vias using synchrotron x-ray diffraction

[Xi Liu, Paragkumar A. Thadesar, Christine L. Taylor, Martin Kunz, Nobumichi Tamura et al.](#)

Citation: [J. Appl. Phys.](#) **114**, 064908 (2013); doi: 10.1063/1.4818327

View online: <http://dx.doi.org/10.1063/1.4818327>

View Table of Contents: <http://jap.aip.org/resource/1/JAPIAU/v114/i6>

Published by the [AIP Publishing LLC](#).

---

### Additional information on *J. Appl. Phys.*

Journal Homepage: <http://jap.aip.org/>

Journal Information: [http://jap.aip.org/about/about\\_the\\_journal](http://jap.aip.org/about/about_the_journal)

Top downloads: [http://jap.aip.org/features/most\\_downloaded](http://jap.aip.org/features/most_downloaded)

Information for Authors: <http://jap.aip.org/authors>

### ADVERTISEMENT

An advertisement for Physics Today Bookends. It features four small portraits of authors: a man in a suit, a woman with blonde hair, a man with glasses, and a man in a white shirt. The 'physics today' logo is in the bottom right. Below the portraits, the text 'Read author interviews in **Bookends**' is displayed.

# Dimension and liner dependent thermomechanical strain characterization of through-silicon vias using synchrotron x-ray diffraction

Xi Liu,<sup>1</sup> Paragkumar A. Thadesar,<sup>2</sup> Christine L. Taylor,<sup>1</sup> Martin Kunz,<sup>3</sup> Nobumichi Tamura,<sup>3</sup> Muhammed S. Bakir,<sup>2</sup> and Suresh K. Sitaraman<sup>1,a)</sup>

<sup>1</sup>*The George W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology, Atlanta, Georgia 30332, USA*

<sup>2</sup>*School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, Georgia 30332, USA*

<sup>3</sup>*Advanced Light Source, Lawrence Berkeley National Laboratory, Berkeley, California 94720, USA*

(Received 7 June 2013; accepted 29 July 2013; published online 12 August 2013)

Strain measurements are demonstrated for through-silicon vias (TSVs) using synchrotron x-ray diffraction to characterize the effect of copper via dimensions and liner materials. Reduction in strains in the silicon around TSVs is observed for the TSVs with smaller via diameters and the TSVs with a thicker polymer liner. To interpret the measured two-dimensional (2D) TSV strain distribution maps of the three-dimensional (3D) TSV strains, a data averaging method based on the energy dependent x-ray absorption is implemented along with additional considerations from the sample preparation by means of an indirect comparison methodology. © 2013 AIP Publishing LLC. [<http://dx.doi.org/10.1063/1.4818327>]

## I. INTRODUCTION

To attain a high-bandwidth and low-energy communication between integrated circuits (ICs), 2.5-dimensional (2.5D) and 3-dimensional (3D) integration with through-silicon vias (TSVs) are widely explored.<sup>1</sup> TSVs commonly consist of copper vias isolated from silicon using a thin (<1 μm) silicon dioxide layer. However, the coefficient of thermal expansion (CTE) mismatch between the copper and the surrounding silicon results into TSV thermomechanical reliability issues.<sup>2–4</sup> To measure TSV stress/strain and understand the thermomechanical reliability issues, micro-Raman spectroscopy, bending beam technique, indentation, and x-ray micro-diffraction have been reported in the literature.<sup>5–9</sup> Moreover, to reduce TSV stress and improve reliability, various modeling results have been pointed towards smaller via diameters or thicker (polymer) liners in the literature.<sup>2,10,11</sup> However, experimental measurements comparing strains in TSVs with different dimensions and liner materials have not been performed as yet. This paper demonstrates experimental characterization and comparison of strains in the silicon around TSVs with different dimensions and liner materials using synchrotron x-ray diffraction (XRD). A beam intensity based data averaging method is applied with the assistance of finite-element modeling (FEM) to interpret the measured two-dimensional (2D) strain distribution maps of the strains in 3D structures.<sup>12</sup>

## II. SAMPLE PREPARATION AND SYNCHROTRON XRD MEASUREMENTS

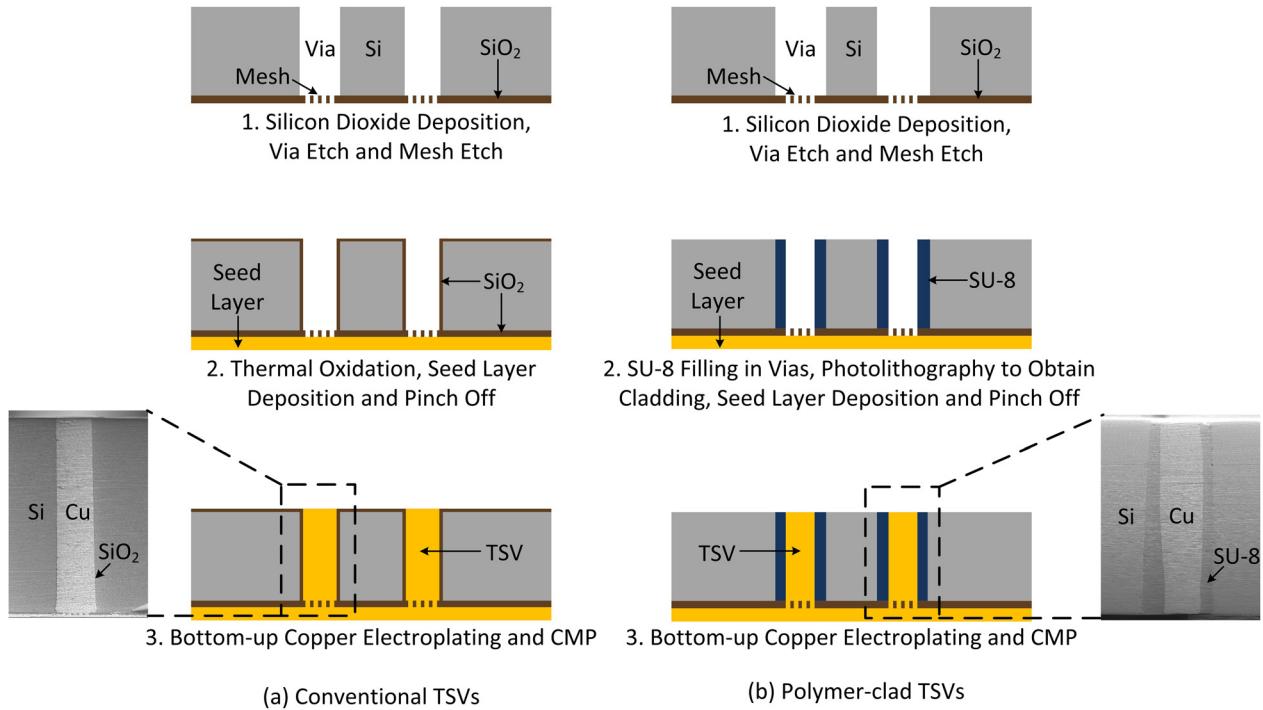

TSVs were fabricated with silicon dioxide and photodefined polymer (SU-8) liners. With respect to the fabrication of TSVs with silicon dioxide liner,<sup>13</sup> a silicon dioxide layer was deposited on one side of a silicon wafer, as shown in

Fig. 1. Vias were etched in the silicon wafer using anisotropic etching, followed by the etching of a group of micro-vias, called mesh,<sup>13</sup> in the suspended silicon dioxide layer at the base of the vias. Thermal oxidation was performed as a next step followed by a titanium-copper seed layer deposition over the silicon dioxide layer at the mesh end of the vias. After seed layer deposition, copper electroplating was performed to pinch off the openings in the mesh. Once the mesh openings were pinched off, bottom up copper electroplating of the vias was performed followed by chemical-mechanical polishing (CMP) to remove overburden copper. TSVs with polymer liner<sup>14</sup> were fabricated with mesh, similar to the TSVs with silicon dioxide liner. SU-8 was spin coated to fill the etched vias and photolithography of the SU-8 was performed to obtain a thick polymer liner. Once the polymer liner was fabricated, titanium-copper seed layer deposition over the silicon dioxide layer at the mesh end, mesh pinch off, bottom up TSV copper electroplating, and CMP were performed.

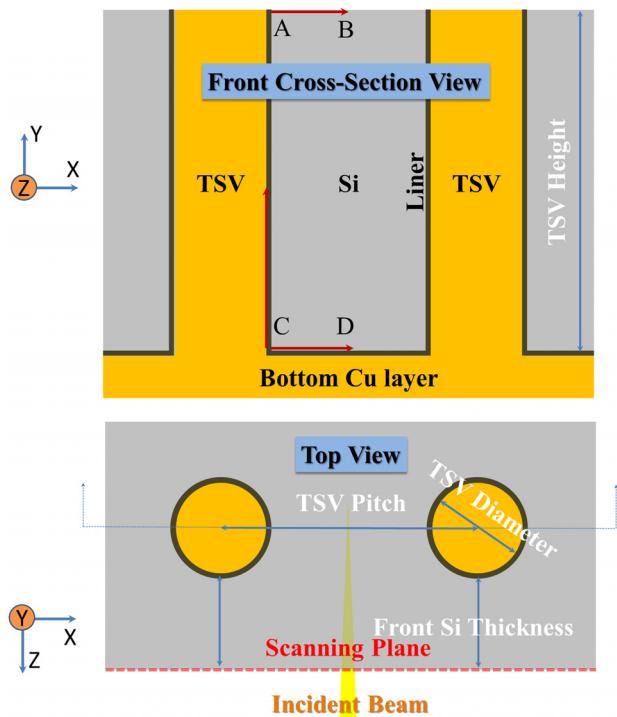

The dimensions of the fabricated TSV samples are shown in Table I. Once the TSV samples were fabricated, cross-section polishing was performed until a specifically defined amount of silicon was left in front of the first row of TSVs to preserve the TSV/silicon mechanical boundary condition, as shown in Fig. 2.

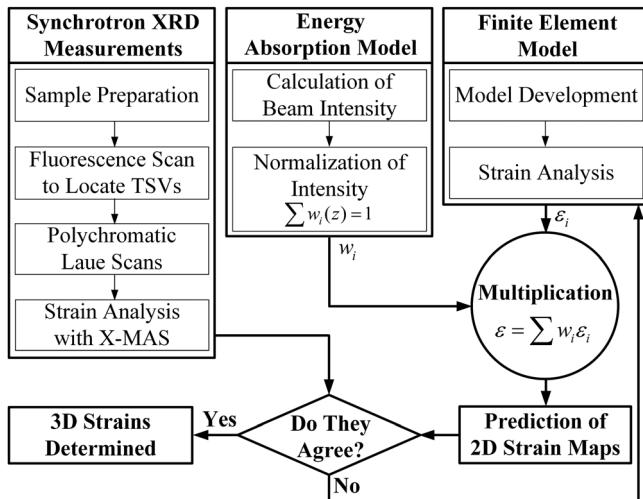

Synchrotron XRD measurements were performed on the fabricated TSV samples at beamline 12.3.2 at the Advanced Light Source (ALS), Lawrence Berkeley National Laboratory (LBNL). Before the test, samples were mounted on a high-precision stage,<sup>15</sup> with the scanning plane being tilted 45° from the incident beam. As shown in Fig. 3, X-ray fluorescence scans were initially conducted on the scanning plane to locate target TSVs. A polychromatic Laue diffraction scan (5–22 keV) was then performed at 150 °C to measure the deviatoric strain distribution, followed by a hydrostatic strain measurement of the TSVs at multiple

<sup>a)</sup>Electronic mail: suresh.sitaraman@me.gatech.edu

FIG. 1. TSV fabrication processes.

locations on the scanning plane using monochromatic step scans across selected Laue diffraction spot (0.01 keV steps). However, due to limited information obtained from the monochromatic scans of the selected locations, only deviatoric strain distributions were analyzed for the entire TSV scanning plane. The x-ray beam was focused to a 1  $\mu\text{m}$  size via a pair of elliptically bent Kirkpatrick-Baez mirrors. Laue pattern data analysis and monochromatic powder diffraction analysis were carried out using X-ray Microdiffraction Analysis Software (X-MAS)<sup>16,17</sup> to calculate the full strain tensor. Before performing the strain measurements, the TSV samples were heated at 150  $^{\circ}\text{C}$  for 1 h to stabilize.

### III. METHODOLOGY, RESULTS AND STRAIN COMPARISON

#### A. Beam-intensity based averaging method

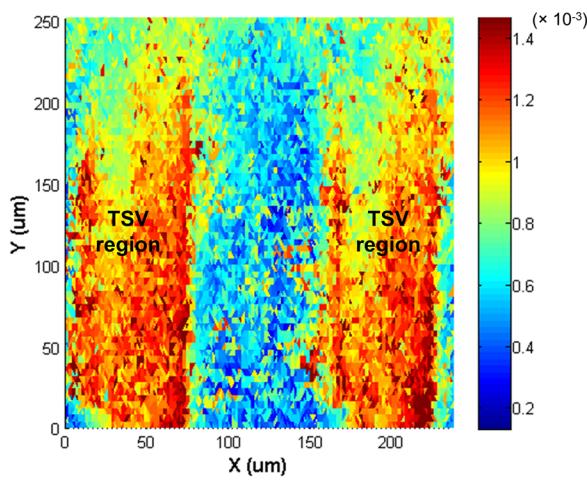

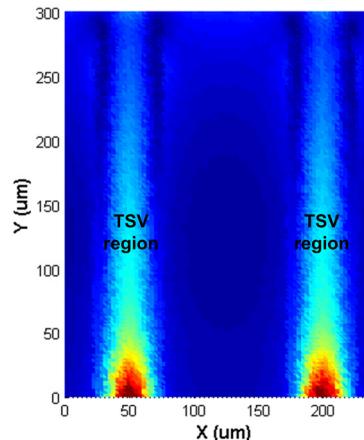

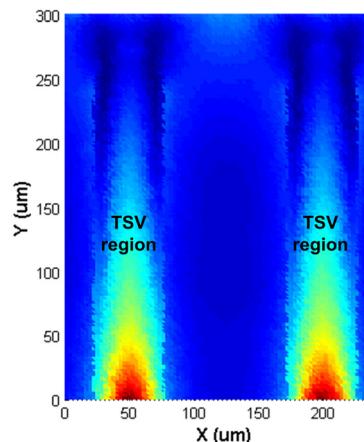

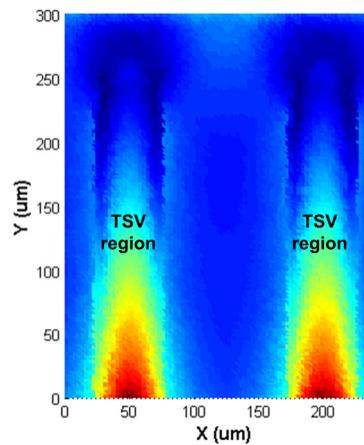

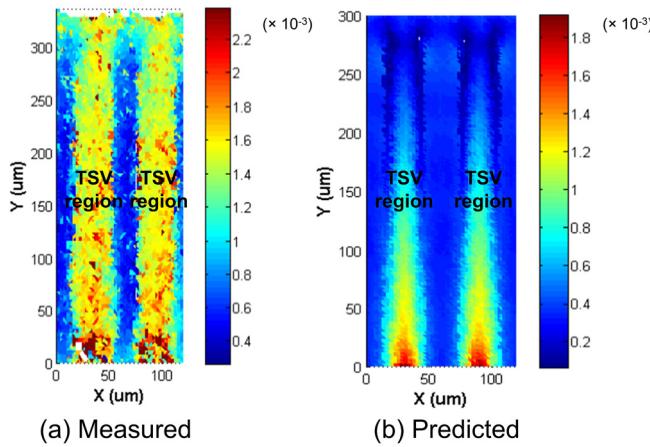

As shown in the measured 2D map of the equivalent deviatoric strain  $\epsilon'_{eq}$  (Eq. (1)) of silicon for sample S2 (Fig. 4), highly stressed regions are recognizable near TSVs. However, the 2D strain map actually represents 3D strain distributions in the silicon around TSVs. To interpret the 2D strain map, an averaging method based on energy dependent

beam absorption was proposed.<sup>12</sup> Since the TSV critical failures are mainly caused by cohesive cracks in silicon and interfacial separation between the copper and the silicon,<sup>3</sup> silicon was selected as the material of interest. In this method, as shown in Fig. 3, the fluxes corresponding to the beam intensities in the silicon are calculated and then normalized to form the white beam intensity weight function  $w(z)$ , where  $\sum w_i(z) = 1$ . Simultaneously, finite element

FIG. 2. Schematic view of a representative TSV array.

TABLE I. Dimensions of the fabricated TSVs.

| Sample No.                           | S1               | S2               | S3               | S4   |

|--------------------------------------|------------------|------------------|------------------|------|

| TSV diameter ( $\mu\text{m}$ )       | 30               | 50               | 80               | 80   |

| TSV pitch ( $\mu\text{m}$ )          | 60               | 150              | 250              | 250  |

| TSV height ( $\mu\text{m}$ )         | 300              | 300              | 390              | 390  |

| Front Si thickness ( $\mu\text{m}$ ) | 13               | 50               | 55               | 40   |

| Liner thickness ( $\mu\text{m}$ )    | 1                | 1                | 1                | 25   |

| Liner material                       | SiO <sub>2</sub> | SiO <sub>2</sub> | SiO <sub>2</sub> | SU-8 |

FIG. 3. Procedure for experimental measurements and analysis.

TSV array models are built with the same geometry (Table I) and materials (Table II) as the tested TSV samples. The Ti layer at the base of the TSVs is considerably thinner (30 nm)

TABLE II. Material properties.<sup>3,18,19</sup>

|                       | Cu   | Si    | SiO <sub>2</sub> | SU-8 |

|-----------------------|------|-------|------------------|------|

| Young's modulus (GPa) | 70   | 130.9 | 71.4             | 4.02 |

| Poison ratio          | 0.3  | 0.28  | 0.16             | 0.22 |

| CTE (ppm/°C)          | 17.3 | 2.6   | 0.5              | 52   |

compared to the TSV dimensions and is not considered in the models. To capture the process-induced stresses of the TSV samples, the thermal profiles of the aforementioned fabrication processes (Fig. 1) are sequentially applied to the models. To mimic the sequential fabrication process, all the materials are activated sequentially at their process stress-free temperature through the ANSYS<sup>TM</sup> element birth-and-death approach. Thereafter, the deviatoric strain components at 150 °C along the beam penetration direction are extracted and multiplied by the beam intensity based weight function ( $\varepsilon = \sum w_i \varepsilon_i$ ) to get a strain value at any given point on the scanning plane. This process is repeated until all the points on the scanning plane are covered to form a 2D strain map,

$$\varepsilon'_{eq} = \frac{2}{3} \sqrt{\frac{(\varepsilon'_{xx} - \varepsilon'_{yy})^2 + (\varepsilon'_{yy} - \varepsilon'_{zz})^2 + (\varepsilon'_{zz} - \varepsilon'_{xx})^2 + 6(\varepsilon'_{xy}^2 + \varepsilon'_{yz}^2 + \varepsilon'_{xz}^2)}{2}}. \quad (1)$$

## B. Indirect comparison methodology

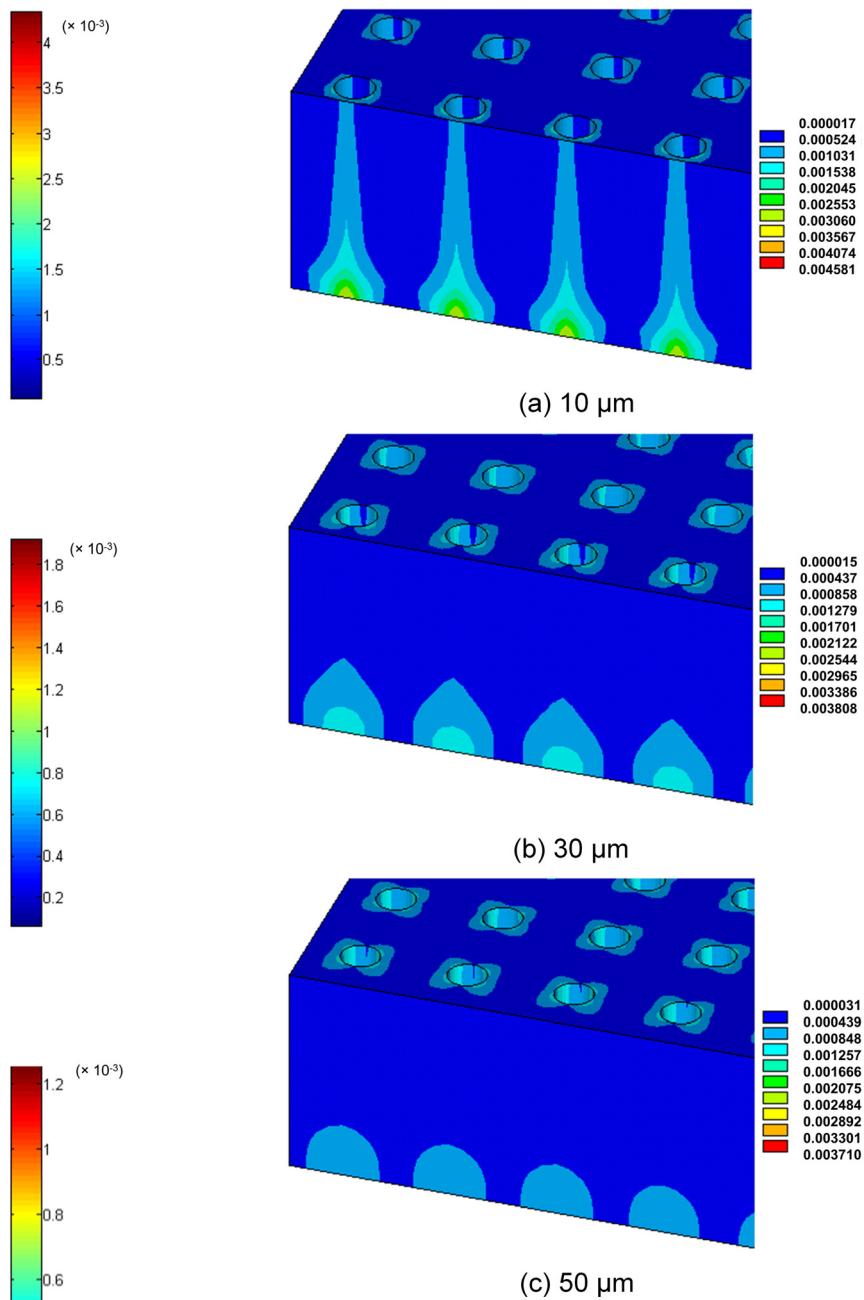

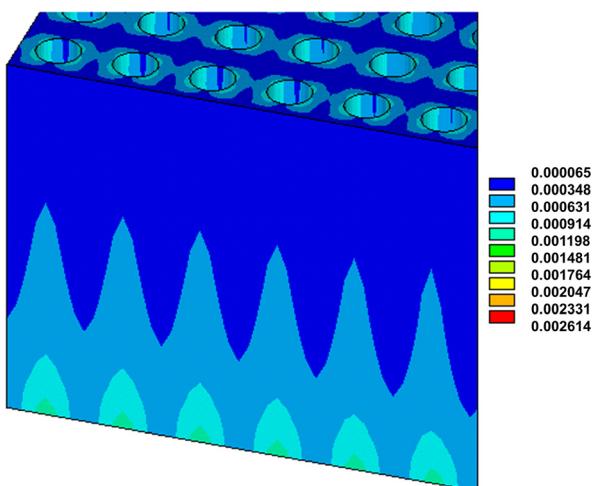

As discussed in Sec. II, a finite thickness of silicon was kept unpolished in front of the first row of TSVs and called the front silicon thickness as shown in Fig. 2. The front silicon thickness for each sample was determined by TSV diameter and pitch to preserve the mechanical boundary condition. The front silicon thicknesses affect the measured 2D strain maps in several ways. First, the dimension dependent mechanical boundary conditions of the TSVs near the scanning plane change with varying front silicon thicknesses. Second, the different front silicon thicknesses affect the

x-ray penetration depth and consequently affect the captured strain information along the penetration depth.<sup>12</sup>

Taking sample S2 as an example, as shown in Fig. 5, the models predict that different front silicon thicknesses result in different 2D strain distribution maps and magnitudes, with strains increasing as the front silicon thickness decreases. Moreover, the 2D FEM results in Fig. 6 show higher strain in the front silicon as the front silicon thickness reduces. In addition, the strain near the front section has larger contribution to the final 2D strain distribution maps. The samples with thicker front silicon have larger contribution from the volume of the lower strained front silicon (Fig. 6(c)) and thus their averaged 2D strain distribution maps show lower strain values, as shown in Fig. 5(c). Therefore, it is essential to take the effect of the front silicon thickness into consideration when we use the 2D strain distribution maps obtained from synchrotron XRD measurements in order to realistically compare different TSV designs, in order to avoid front silicon thickness induced artifacts. One example is the comparison of the measured strain maps of sample S1 in Fig. 7(a) and sample S2 in Fig. 4. Direct comparison of their 2D strain distribution maps shows that sample S1 is under higher thermomechanical strain than sample S2. This conclusion is incorrect since sample S2 has larger diameter copper vias than sample S1. Sample S2 is expected to experience larger CTE mismatch induced thermomechanical strains,<sup>2</sup> as evidenced by the comparison of Figs. 6(c) and 8.

To address this issue, an indirect approach is applied by using the measured 2D strain distribution maps to calibrate a

FIG. 4. Measured sample S2 2D  $\varepsilon'_{eq}$  distribution map of silicon at 150 °C.

(a) 10 μm

(b) 30 μm

(c) 50 μm

FIG. 5. Predicted sample S2 2D  $\epsilon'_{eq}$  maps with different front silicon thickness at 150 °C.

3D finite element analysis (FEA) model (Fig. 3), and then the calculated strain from the 3D FEA model is used to compare different TSV designs. To calibrate the 3D FEA models, the aforementioned beam intensity based data averaging method is applied to project the 3D strain distribution from the 3D FEA models onto 2D strain distribution maps. This allows a direct comparison between the measured and the

FIG. 6. Predicted sample S2  $\epsilon'_{eq}$  3D distribution with different front silicon thickness at 150 °C.

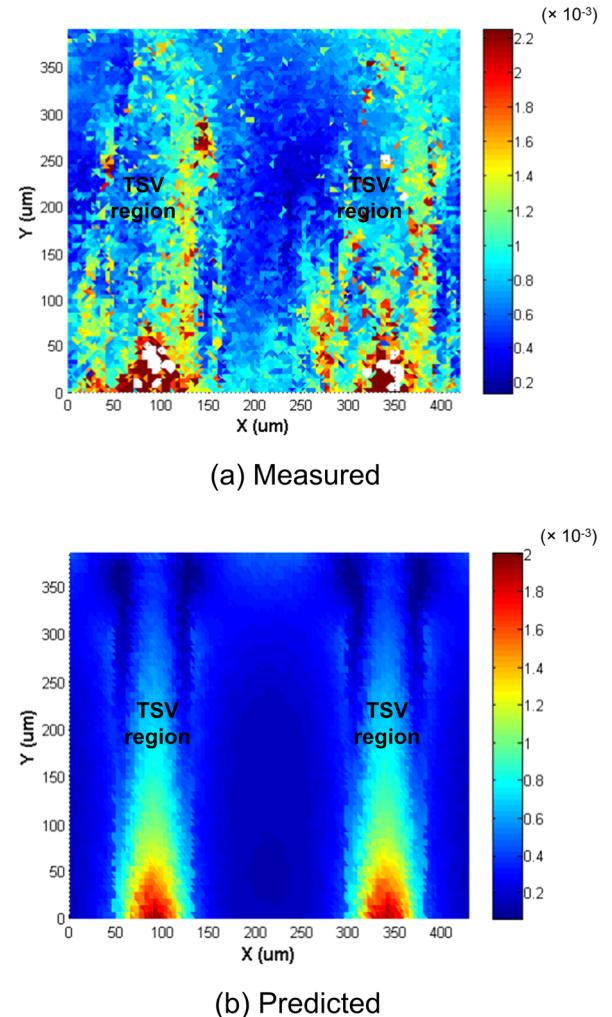

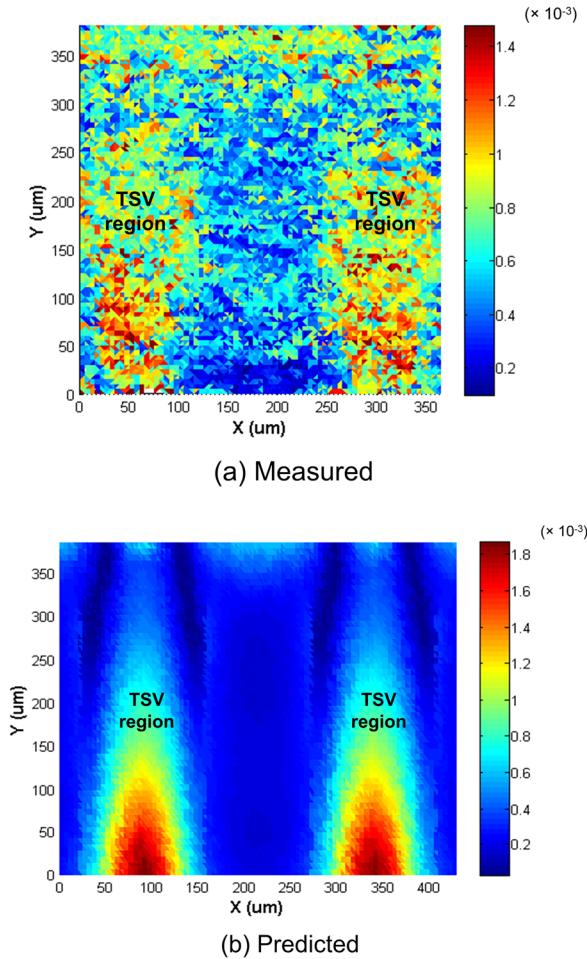

predicted strain data. Fig. 7 compares the measured strain map with the predicted strain map for sample S1; Figs. 4 and 5(c) for sample S2; Fig. 9 for sample S3; Fig. 10 for sample S4. The comparison shows that the model results generally agree well with the measurement data on strain distribution. The remaining discrepancies are due to the following reasons. First, it is observed that while repeating the measurements on the same sample, a few measured values differed from the modeled values due to the stress history during the high temperature measurements. Second, the finite element model considers an ideal thermal loading case without accounting for the fabrication induced defects and copper grain coarsening during the fabrication. Even with the discrepancies in some of the strain magnitudes, both the

FIG. 7. Measured and predicted sample S1 2D  $\varepsilon'_{eq}$  distribution map of silicon at 150 °C.

modeled and measured strain distribution trends matched well for all the four samples, and the trends are useful to identify critical locations in the silicon.

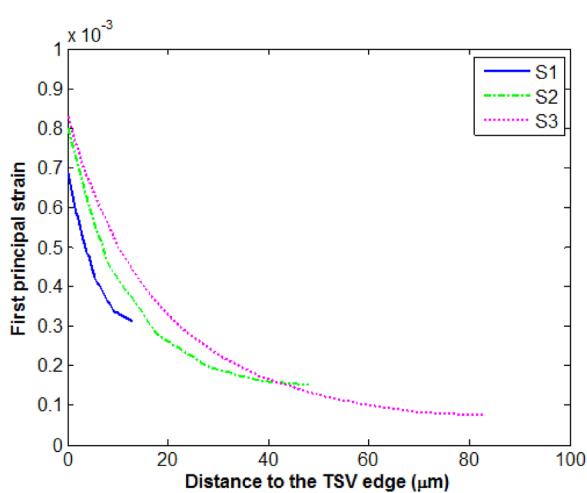

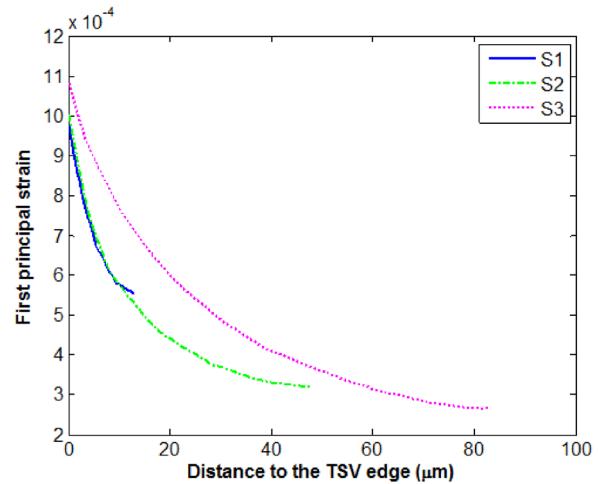

### C. Effect of TSV dimensions

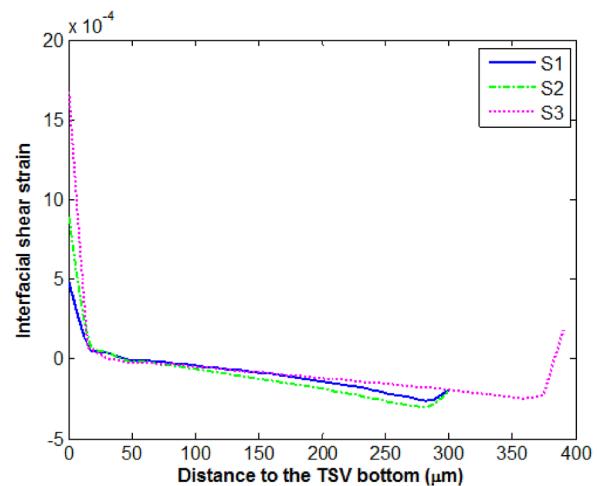

To study the effect of TSV dimensions on TSV thermomechanical reliability, samples S1, S2, and S3 are compared. They have different TSV diameter, pitch, and height, but the same fabrication process, liner material (silicon dioxide), and liner thickness (1  $\mu$ m). Since the dominating TSV thermomechanical failure modes are silicon cracking and copper/liner separation,<sup>3</sup> the first principal strain  $\varepsilon_{11}$  in the silicon and the copper/liner interfacial shear strain are compared. As shown in Figs. 11 and 12, the CTE mismatch between silicon and copper induces high strain near the TSV edges. The strain decreases quickly and then levels off when moving away. Larger copper via diameter generally results in higher strain in the surrounding silicon, thus making the silicon more prone to cracking. The existence of a bottom copper layer causes even higher strain in the silicon near the TSV bottom (path C-D in Fig. 2) than near the TSV top

FIG. 8. Predicted sample S1 3D  $\varepsilon'_{eq}$  distribution of silicon at 150 °C.

FIG. 9. Measured and predicted sample S3 2D  $\varepsilon'_{eq}$  distribution map of silicon at 150 °C.

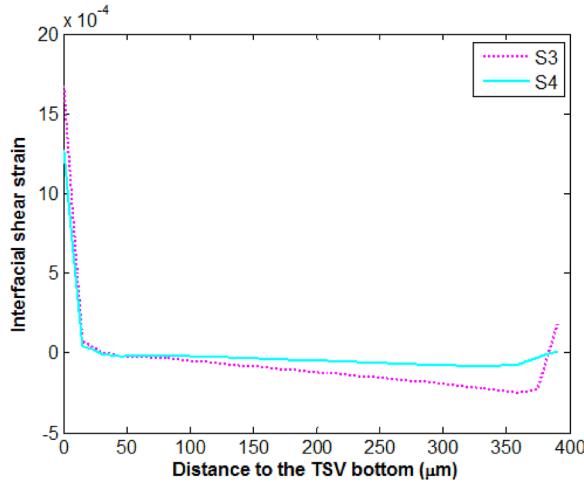

(path A-B in Fig. 2). To investigate the possibility of interfacial separation at the copper/liner interfaces, the interfacial shear strain  $\varepsilon_{xy}$  along the TSV side wall of the cross-section (path C-A in Fig. 2) are plotted in Fig. 13. It shows that high interfacial shear strain occurs near the TSV top and bottom, especially near the bottom due to the presence of the bottom copper layer. Similarly, a larger TSV diameter induces higher interfacial shear strain, and consequently is more likely to cause copper/liner separation. These copper/liner interfacial separations can be observed in the previous test results.<sup>3</sup>

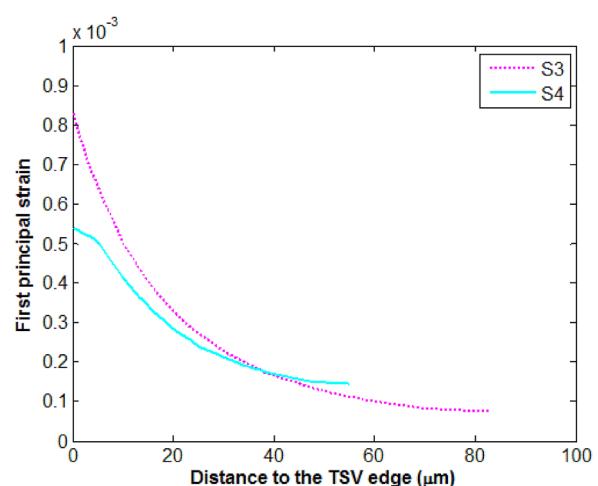

### D. Effect of liner material

To study the effect of liner material on the thermomechanical reliability of TSVs, sample S4 with a thick (25  $\mu$ m) SU-8 liner is compared to sample S3 with the same copper via dimensions but with a thin (1  $\mu$ m) silicon dioxide liner. Fig. 14 shows that the thick SU-8 liner serves as a cushion layer, reducing the thermomechanical force applied to the surrounding silicon as the copper via expands at a high temperature. Also, as shown in Fig. 15, the SU-8 liner mitigates the interfacial shear strain, and thus reduces the possibilities of interfacial separation.

FIG. 10. Measured and predicted sample S4 2D  $\epsilon'_{eq}$  distribution map of silicon at 150 °C.

#### IV. CONCLUSION

In this paper, TSVs with different dimensions and liner material have been fabricated and measured at 150 °C using synchrotron XRD. To interpret the measured 2D strain distribution maps, a beam intensity based data averaging method

FIG. 11. Predicted first principal strain  $\epsilon_{11}$  of silicon along path A-B at 150 °C.

FIG. 12. Predicted first principal strain  $\epsilon_{11}$  of silicon along path C-D at 150 °C.

FIG. 13. Predicted interfacial shear strain  $\epsilon_{xy}$  along copper/liner interface C-A at 150 °C.

FIG. 14. Predicted first principal strain  $\epsilon_{11}$  of silicon along path A-B at 150 °C.

FIG. 15. Predicted interfacial shear strain  $\varepsilon_{xy}$  along copper/liner interface C-A at 150 °C.

has been applied. The analysis shows that a direct comparison of the measured 2D strain distribution maps of different TSV samples may yield results dependent on artifacts related to sample preparation. Thus, an indirect comparison approach based on experimentally calibrated FEA calculations is adopted. Comparisons show that TSVs with larger diameter generally induce higher strain in the silicon as well as at the copper/liner interface, thus have more reliability issues. This is promising in view of the current trend for smaller dimensions of TSVs in terms of thermomechanical strain induced reliability concerns. Moreover, TSVs with thick SU-8 liner experience lower strains compared to TSVs with thin silicon dioxide liner.

## ACKNOWLEDGMENTS

This work is supported by the Semiconductor Research Corporation under Contract No. 2012-KJ-2255. The Advanced Light Source (ALS) is supported by the Director, Office of Science, Office of Basic Energy Sciences, of the U.S. Department of Energy under Contract No. DE-AC02-

05CH11231 at the Lawrence Berkeley National Laboratory (LBNL).

- <sup>1</sup>J. U. Knickerbocker, P. S. Andry, B. Dang, R. R. Horton, M. J. Interrante, C. S. Patel, R. J. Polastre, K. Sakuma, R. Sirdeshmukh, E. J. Sprogis, S. M. Sri-Jayantha, A. M. Stephens, A. W. Topol, C. K. Tsang, B. C. Webb, and S. L. Wright, *IBM J. Res. Dev.* **52**, 553 (2008).

- <sup>2</sup>X. Liu, M. Simmons-Matthews, K. P. Wachtler, and S. K. Sitaraman, *Proceedings of ASME International Mechanical Engineering Congress and Exposition (IMECE), Denver, Colorado, USA, 11–17 November (2011)*, pp. 903–910.

- <sup>3</sup>X. Liu, Q. Chen, V. Sundaram, R. R. Tummala, and S. K. Sitaraman, *Microelectron. Reliab.* **53**, 70 (2013).

- <sup>4</sup>K. N. Tu, *Microelectron. Reliab.* **51**, 517 (2011).

- <sup>5</sup>I. D. Wolf, V. Simons, V. Cherman, R. Labie, B. Vandevelde, and E. Beyne, in *Proceedings of 62nd IEEE Electronic Components and Technology Conference (ECTC), San Diego, CA, 29 May–1 June (USA, 2012)*, pp. 331–337.

- <sup>6</sup>S. K. Ryu, Q. Zhao, M. Hecker, H. Y. Son, K. Y. Byun, J. Im, P. S. Ho, and R. Huang, *J. Appl. Phys.* **111**, 063513 (2012).

- <sup>7</sup>S. K. Ryu, T. Jiang, K. H. Lu, J. Im, H. Y. Son, B. Kwang-Yoo, R. Huang, and P. S. Ho, *Appl. Phys. Lett.* **100**, 041901 (2012).

- <sup>8</sup>G. Lee, M. J. Choi, S. W. Jeon, K. Y. Byun, and D. Kwon, *Proceedings 62nd IEEE Electronic Components and Technology Conference (ECTC), San Diego, CA, 29 May–1 June USA (2012)*, pp. 781–786.

- <sup>9</sup>A. S. Budiman, H. A. S. Shin, B. J. Kim, S. H. Hwang, H. Y. Son, M. S. Suh, Q. H. Chung, K. Y. Byun, N. Tamura, M. Kunz, and Y. C. Joo, *Microelectron. Reliab.* **52**, 530 (2012).

- <sup>10</sup>S. K. Ryu, K. H. Lu, X. Zhang, J. H. Im, P. S. Ho, and R. Huang, *IEEE Trans. Device Mater. Reliab.* **11**, 35 (2011).

- <sup>11</sup>Z. Chen, X. Song, and S. Liu, in *Proceedings of the 59th IEEE Electronic Components and Technology Conference (ECTC), San Diego, CA, 26–29 May USA (2009)*, pp. 1374–1380.

- <sup>12</sup>X. Liu, P. A. Thadesar, C. L. Taylor, M. Kunz, N. Tamura, M. S. Bakir, and S. K. Sitaraman, *Appl. Phys. Lett.* **103**, 022107 (2013).

- <sup>13</sup>J. H. Lai, H. S. Yang, H. Chen, C. R. King, J. Zaveri, R. Ravindran, and M. S. Bakir, *J. Micromech. Microeng.* **20**, 025016 (2010).

- <sup>14</sup>P. A. Thadesar and M. S. Bakir, *IEEE Trans. Compon., Packag., Manuf. Technol.* **3**, 1130 (2013).

- <sup>15</sup>M. Kunz, N. Tamura, C. Kai, A. A. MacDowell, R. S. Celestre, M. M. Church, S. Fakra, E. E. Domning, J. M. Glossinger, J. L. Kirschman, G. Y. Morrison, D. W. Plate, B. V. Smith, T. Warwick, V. V. Yashchuk, H. A. Padmore, and E. Ustundag, *Rev. Sci. Instrum.* **80**, 035108 (2009).

- <sup>16</sup>J. S. Chung and G. E. Ice, *J. Appl. Phys.* **86**, 5249 (1999).

- <sup>17</sup>N. Tamura, A. A. MacDowell, R. Spolenak, B. C. Valek, J. C. Bravman, W. L. Brown, R. S. Celestre, H. A. Padmore, B. W. Batterman, and J. R. Patel, *J. Synchrotron. Radiat.* **10**, 137 (2003).

- <sup>18</sup>D. T. Read, Y. W. Cheng, and R. Geiss, *Microelectron. Eng.* **75**, 63 (2004).

- <sup>19</sup>A. D. Campo and C. Greiner, *J. Micromech. Microeng.* **17**, R81 (2007).